# TLC3544, TLC3548 5-V ANALOG, 3-/5-V DIGITAL, 14-BIT, 200-KSPS, 4-/8-CHANNELS SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH 0-5 V (PSEUDODIFFERENTIAL) INPUTS

SLAS266C - OCTOBER 2000 - REVISED MAY 2003

#### 14-Bit Resolution

- Maximum Throughput 200 KSPS

- Analog Input Range 0-V to Reference Voltage

- Multiple Analog Inputs:

- 8 Channels for TLC3548

- 4 Channels for TLC3544

- Pseudodifferential Analog Inputs

- SPI/DSP-Compatible Serial Interfaces With SCLK up to 25 MHz

- Single 5-V Analog Supply; 3-/5-V Digital Supply

- Low Power:

- 4 mA (Internal Reference: 1.8 mA) for Normal Operation

- 20 μA in Autopower-Down

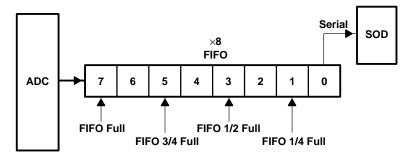

- Built-In 4-V Reference, Conversion Clock and 8x FIFO

- Hardware-Controlled and Programmable Sampling Period

- Programmable Autochannel Sweep and Repeat

- Hardware Default Configuration

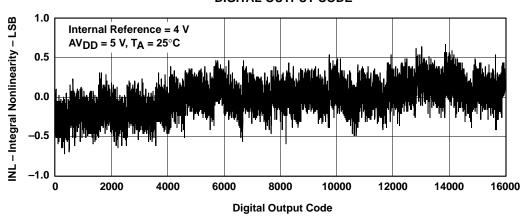

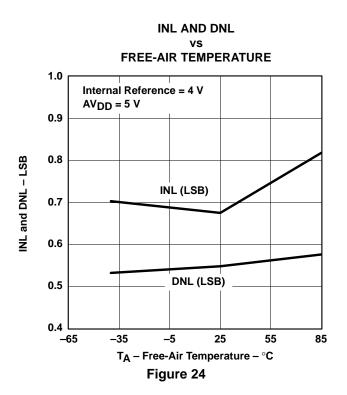

INL: ±1 LSB Max

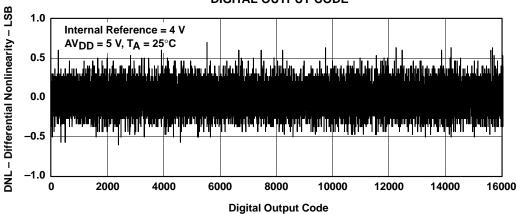

DNL: ±1 LSB Max

SINAD: 80.8 dB

THD: -95 dB

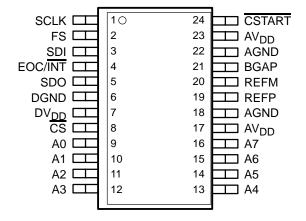

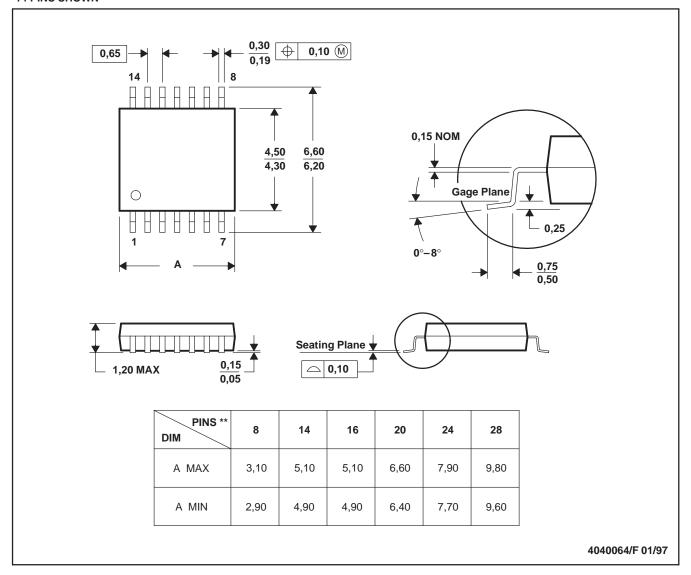

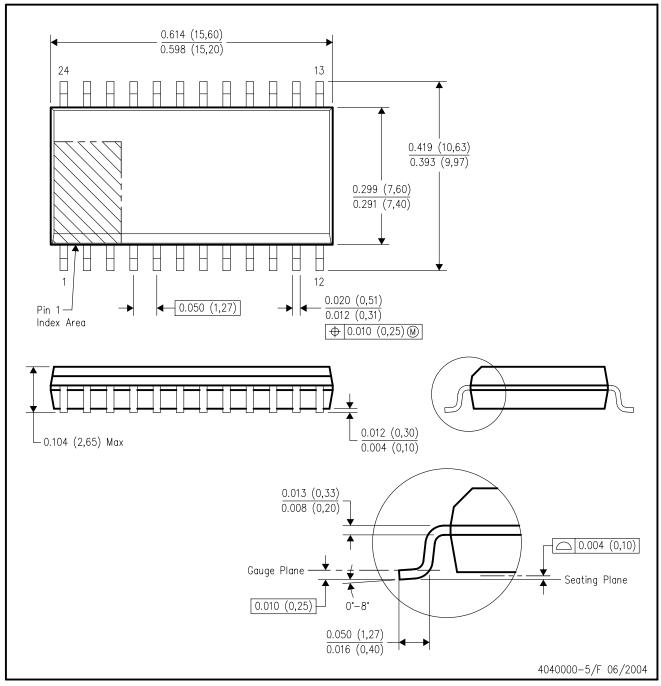

#### TLC3548 DW OR PW PACKAGE (TOP VIEW)

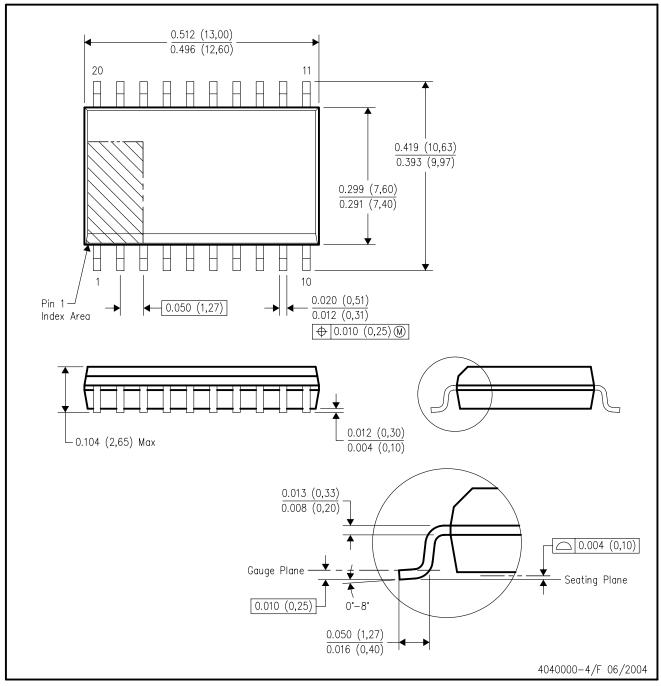

#### TLC3544 DW OR PW PACKAGE (TOP VIEW)

#### description

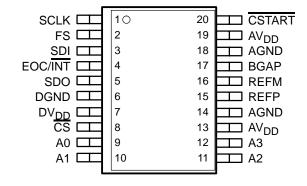

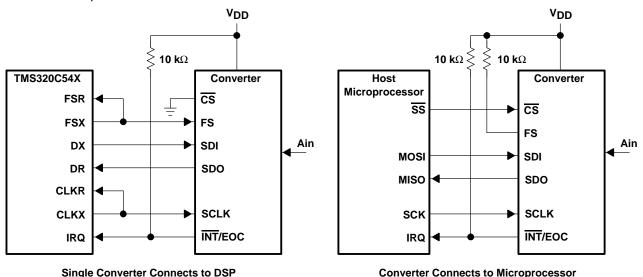

The TLC3544 and TLC3548 are a family of 14-bit resolution high-performance, low-power, CMOS analog-to-digital converters (ADC). All devices operate from a single 5-V analog power supply and 3-V to 5-V digital supply. The serial interface consists of four digital inputs [chip select ( $\overline{CS}$ ), frame sync (FS), serial input-output clock (SCLK), serial data input (SDI)], and a 3-state serial data output (SDO).  $\overline{CS}$  (works as  $\overline{SS}$ , slave select), SDI, SDO, and SCLK form an SPI interface. FS, SDI, SDO, and SCLK form a DSP interface. The frame sync signal (FS) indicates the start of a serial data frame being transferred. When multiple converters connect to one serial port of a DSP,  $\overline{CS}$  works as the chip select to allow the host DSP to access the individual converter.  $\overline{CS}$  can be tied to ground if only one converter is used. FS must be tied to DV<sub>DD</sub> if it is not used (such as in an SPI interface). When SDI is tied to DV<sub>DD</sub>, the device is set in hardware default mode after power-on, and no software configuration is required. In the simplest case, only three wires (SDO, SCLK, and  $\overline{CS}$  or FS) are needed to interface with the host.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# description (continued)

SLAS266C - OCTOBER 2000 - REVISED MAY 2003

In addition to being a high-speed ADC with versatile control capability, these devices have an on-chip analog multiplexer (MUX) that can select any analog input or one of three self-test voltages. The sample-and-hold function is automatically started after the fourth SCLK (normal sampling) or can be controlled by  $\overline{CSTART}$  to extend the sampling period (extended sampling). The normal sampling period can also be programmed as short sampling (12 SCLKs) or long sampling (44 SCLKs) to accommodate the faster SCLK operation popular among high-performance signal processors. The TLC3544 and TLC3548 are designed to operate with low power consumption. The power saving feature is further enhanced with software power-down/ autopower-down modes and programmable conversion speeds. The conversion clock (internal OSC) is built in. The converter can also use an external SCLK as the conversion clock for maximum flexibility. The TLC3544 and TLC3548 have a 4-V internal reference. The converters are specified with unipolar input range of 0-V to 5-V when a 5-V external reference is used.

#### **AVAILABLE OPTIONS**

| TA            | 20-TSSOP 20-SOIC (PW) (DW) |            | 24-SOIC<br>(DW) | 24-TSSOP<br>(PW) |

|---------------|----------------------------|------------|-----------------|------------------|

| 0°C to 70°C   | TLC3544CPW                 | TLC3544CDW | TLC3548CDW      | TLC3548CPW       |

| -40°C to 85°C | TLC3544IPW                 | TLC3544IDW | TLC3548IDW      | TLC3548IPW       |

#### functional block diagram

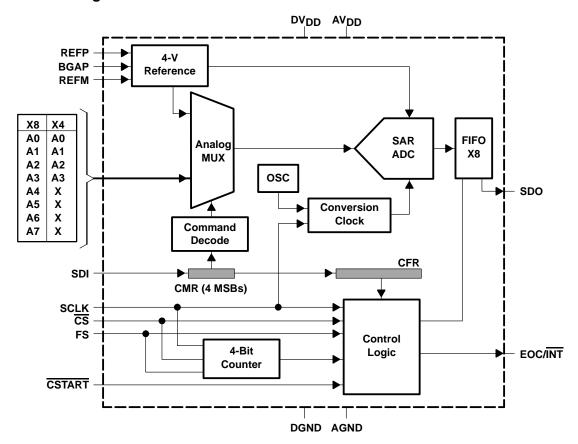

#### equivalent input circuit

Diode Turn on Voltage: 35 V

**Equivalent Digital Input Circuit**

#### **Equivalent Analog Input Circuit**

#### **Terminal Functions**

| TERMINAL             |                                              |                                                                                                                                                                                               |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO.             |                                              |                                                                                                                                                                                               |        | 1/0                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                      | TLC3544 TLC3548                              |                                                                                                                                                                                               |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

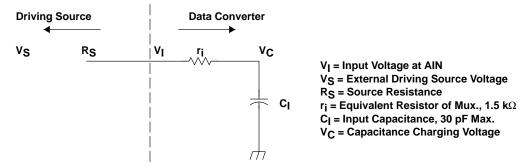

| A0<br>A1<br>A2<br>A3 | A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7 | 10 10 driving source impedance should be less than or equal to 1 kΩ for normal source impedance, use the external hardware conversion start signal $\overline{\text{CSTAF}}$                  |        | Analog signal inputs. Analog input signals applied to these terminals are internally multiplexed. The driving source impedance should be less than or equal to 1 k $\Omega$ for normal sampling. For larger source impedance, use the external hardware conversion start signal $\overline{\text{CSTART}}$ (the low time of $\overline{\text{CSTART}}$ controls the sampling period) or reduce the frequency of SCLK to increase the sampling time. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AGN                  | D                                            | 14, 18                                                                                                                                                                                        | 18, 22 | I                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Analog ground return for the internal circuitry. Unless otherwise noted, all analog voltage measurements are with respect to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $AV_{DI}$            | D                                            | 13, 19                                                                                                                                                                                        | 17, 23 | I                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Analog supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                      |                                              | Internal bandgap compensation pin. Install compensation capacitors between BGAP and AGND. 0.1 $\mu$ F for external reference; 10 $\mu$ F in parallel with 0.1 $\mu$ F for internal reference. |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ĊŚ                   |                                              | 8                                                                                                                                                                                             | 8      | I                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chip select. When $\overline{\text{CS}}$ is high, SDO is in high-impedance state, SDI is ignored, and SCLK is disabled to clock data but works as conversion clock source if programmed. The falling edge of $\overline{\text{CS}}$ input resets the internal 4-bit counter, enables SDI and SCLK, and removes SDO from high-impedance state.  If FS is high at $\overline{\text{CS}}$ falling edge, $\overline{\text{CS}}$ falling edge initiates the operation cycle. $\overline{\text{CS}}$ works as slave select ( $\overline{\text{SS}}$ ) to provide an SPI interface.  If FS is low at $\overline{\text{CS}}$ falling edge, FS rising edge initiates the operation cycle. $\overline{\text{CS}}$ can be used as chip select to allow the host to access the individual converter. |

| CSTART               |                                              | 20                                                                                                                                                                                            | 24     | I                                                                                                                                                                                                                                                                                                                                                                                                                                                   | External sampling trigger signal, which initiates the sampling from a selected analog input channel when the device works in extended sampling mode (asynchronous sampling). A high-to-low transition starts the sampling of the analog input signal. A low-to-high transition puts the S/H in hold mode and starts the conversion. The low time of the CSTART signal controls the sampling period. CSTART signal must be long enough for proper sampling. CSTART must stay high long enough after the low-to-high transition for the conversion to finish maturely. The activation of CSTART is independent of SCLK and the level of CS and FS. However, the first CSTART cannot be issued before the rising edge of the 11th SCLK. Tie this terminal to DVDD if not used.              |

| DGN                  | ID                                           | 6                                                                                                                                                                                             | 6      | ı                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Digital ground return for the internal circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $DV_D$               | D                                            | 7                                                                                                                                                                                             | 7      | I                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Digital supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# **Terminal Functions (Continued)**

| TERMINAL |          |         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|----------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NAME NO. |         | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NAIVIE   | TLC3544  | TLC3548 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| EOC(INT) | 4        | 4       | 0   | End of conversion (EOC) or interrupt to host processor (INT)                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |          |         |     | EOC: used in conversion mode 00 only. EOC goes from high to low at the end of the sampling and remains low until the conversion is complete and data is ready.                                                                                                                                                                                                                                                                                                              |

|          |          |         |     | INT: Interrupt to the host processor. The falling edge of INT indicates data is ready for output. INT is cleared by the following CS↓, FS↑, or CSTART↓.                                                                                                                                                                                                                                                                                                                     |

| FS       | 2        | 2       | I   | Frame sync input from DSP. The rising edge of FS indicates the start of a serial data frame being transferred (coming into or being sent out of the device). If FS is low at the falling edge of $\overline{\text{CS}}$ , the rising edge of FS initiates the operation cycle, resets the internal 4-bit counter, and enables SDI, SDO, and SCLK. Tie this pin to DVDD if FS is not used to initiate the operation cycle.                                                   |

| REFM     | 16       | 20      | ı   | External low reference input. Connect REFM to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| REFP     | 15       | 19      | I   | External positive reference input. When an external reference is used, the range of maximum input voltage is determined by the difference between the voltage applied to this terminal and to the REFM terminal. Always install decoupling capacitors (10 $\mu F$ in parallel with 0.1 $\mu F$ ) between REFP and REFM.                                                                                                                                                     |

| SCLK     | 1        | 1       | -   | Serial clock input from the host processor to clock in the input from SDI and clock out the output via SDO. It can also be used as the conversion clock source when the external conversion clock is selected (see Table 2). When $\overline{CS}$ is low, SCLK is enabled. When $\overline{CS}$ is high, SCLK is disabled for the data transfer, but can still work as the conversion clock source.                                                                         |

| SDI      | 3        | 3       | 1   | Serial data input. The first 4 MSBs, ID[15:12], are decoded as one 4-bit command. All trailing bits, except for the CONFIGURE WRITE command, are filled with zeros. The CONFIGURE WRITE command requires additional 12-bit data. The MSB of input data, ID[15], is latched at the first falling edge of SCLK following FS falling edge, if FS starts the operation, or latched at the falling edge of first SCLK following CS falling edge when CS initiates the operation. |

|          |          |         |     | The remaining input data (if any) is shifted in on the rising edge of SCLK and latched on the falling edge of SCLK. The input via SDI is ignored after the 4-bit counter counts to 16 (clock edges) or a low-to-high transition of $\overline{\text{CS}}$ , whichever happens first. Refer to the timing specification for the timing requirements. Tie SDI to DV <sub>DD</sub> if using hardware default mode (refer to device initialization).                            |

| SDO      | 5        | 5       | 0   | The 3-state serial output for the A/D conversion result. All data bits are shifted out through SDO. SDO is in the high-impedance state when $\overline{CS}$ is high. SDO is released after a $\overline{CS}$ falling edge. The output format is MSB (OD[15]) first.                                                                                                                                                                                                         |

|          |          |         |     | When FS initiates the operation, the MSB of output via SDO, OD[15], is valid before the first falling edge of SCLK following the falling edge of FS.                                                                                                                                                                                                                                                                                                                        |

|          |          |         |     | When $\overline{\text{CS}}$ initiates the operation, the MSB, OD[15], is valid before the first falling edge of SCLK following the $\overline{\text{CS}}$ falling edge.                                                                                                                                                                                                                                                                                                     |

|          |          |         |     | The remaining data bits are shifted out on the rising edge of SCLK and are valid before the falling edge of SCLK. Refer to the timing specification for the details.                                                                                                                                                                                                                                                                                                        |

|          |          |         |     | In a select/conversion operation, the first 14 bits are the results from the previous conversion (data). In READ FIFO operation, the data is from FIFO. In both cases, the last two bits are don't care.                                                                                                                                                                                                                                                                    |

|          |          |         |     | In a WRITE operation, the output from SDO is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |          |         |     | SDO goes into high-impedance state at the sixteenth falling edge of SCLK after the operation cycle is initiated. SDO is in high-impedance state during conversions in modes 01, 10, and 11.                                                                                                                                                                                                                                                                                 |

# TLC3544, TLC3548 5-V ANALOG, 3-/5-V DIGITAL, 14-BIT, 200-KSPS, 4-/8-CHANNELS SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH 0-5 V (PSEUDODIFFERENTIAL) INPUTS

SLAS266C - OCTOBER 2000 - REVISED MAY 2003

## absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage, GND to AV <sub>DD</sub> , DV <sub>DD</sub>                 |                                   |

|----------------------------------------------------------------------------|-----------------------------------|

| Analog input voltage range                                                 | 0.2 V to AV <sub>DD</sub> +0.2 V  |

| Analog input current                                                       | 100 mA MAX                        |

| Reference input voltage                                                    | AV <sub>DD</sub> + 0.3 V          |

| Digital input voltage range                                                | 0.3 V to DV <sub>DD</sub> + 0.3 V |

| Operating virtual junction temperature range, T <sub>J</sub>               | –40°C to 150°C                    |

| Operating free-air industrial temperature range, T <sub>A</sub> : I suffix | –40°C to 85°C                     |

| C suffix                                                                   | 0°C to 70°C                       |

| Storage temperature range, T <sub>sta</sub>                                | –65°C to 150°C                    |

| Lead temperature 1,6 mm (1.16 inch) from case for 10 seconds               | 260°C                             |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

general electrical characteristics over recommended operating free-air temperature range, single-ended input, normal long sampling, 200 KSPS, AV $_{\rm DD}$  = 5 V, external reference (V $_{\rm REFP}$  = 4 V, V $_{\rm REFM}$  = 0 V) or internal reference, SCLK frequency = 25 MHz, fixed channel at CONV mode 00, analog input signal source resistance = 25  $\Omega$  (unless otherwise noted)

| PARAMETER                            |                                  | TEST CONDITIONS                               |                                                                         | MIN                                                  | TYP†      | MAX        | UNIT          |            |        |  |

|--------------------------------------|----------------------------------|-----------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------|-----------|------------|---------------|------------|--------|--|

| Digital Input                        |                                  |                                               |                                                                         |                                                      |           |            |               |            |        |  |

| VIH                                  | High-level contro                | ol input voltage                              | $DV_{DD} = 5 V$<br>$DV_{DD} = 3 V$                                      |                                                      |           | 3.8<br>2.1 |               |            | V      |  |

| V <sub>IL</sub>                      | Low-level contro                 | l input voltage                               | $DV_{DD} = 5 V$<br>$DV_{DD} = 3 V$                                      |                                                      |           |            |               | 0.8        | ٧      |  |

| liн                                  | High-level input                 | current                                       | $V_I = DV_{DD}$                                                         |                                                      |           |            | 0.005         | 2.5        | μΑ     |  |

| I <sub>IL</sub>                      | Low-level input of               | current                                       | V <sub>I</sub> = DGND                                                   |                                                      |           | -2.5       | 0.005         |            | μΑ     |  |

|                                      | Input capacitano                 | е                                             |                                                                         |                                                      |           |            | 20            | 25         | pF     |  |

| Digital output                       |                                  |                                               | •                                                                       |                                                      | •         | •          |               | <u> </u>   |        |  |

| VOН                                  | High-level digital               |                                               | I <sub>O</sub> = -0.2 mA                                                | $DV_{DD} = 5 V$<br>$DV_{DD} = 3 V$                   |           | 4.2<br>2.4 |               |            | V      |  |

| Vol                                  | Low lovel digital output         |                                               | DV <sub>DD</sub> = 5 V                                                  | $I_O = 0.8 \text{ mA}$<br>$I_O = 50 \mu\text{A}$     |           |            |               | 0.4        | V      |  |

| VOL                                  |                                  |                                               | DV <sub>DD</sub> = 3 V                                                  | $I_{O} = 0.8 \text{ mA}$<br>$I_{O} = 50 \mu\text{A}$ |           |            |               | 0.4        | ·      |  |

| loz                                  | Off-state output (high-impedance |                                               | $V_O = DV_{DD}$<br>$V_O = DGND$                                         | CS = DV <sub>DD</sub>                                |           | -1         | 0.02<br>-0.02 | 1          | μΑ     |  |

| Power Supply                         |                                  |                                               |                                                                         |                                                      |           | -          |               |            |        |  |

| AV <sub>DD</sub><br>DV <sub>DD</sub> | Supply voltage                   |                                               |                                                                         |                                                      |           | 4.5<br>2.7 | 5<br>5        | 5.5<br>5.5 | V<br>V |  |

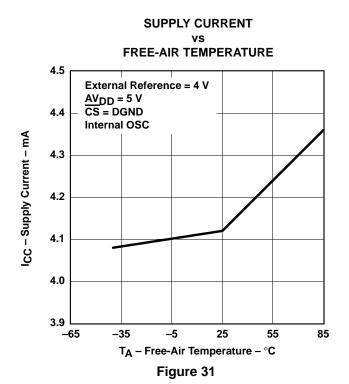

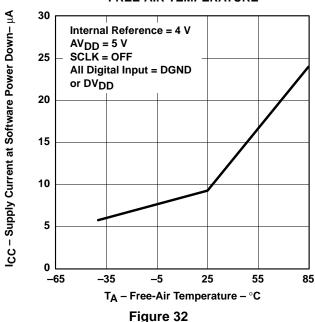

| lcc                                  | Power supply                     | AV <sub>DD</sub> current-                     |                                                                         | ck is internal OS<br>, AVD = 5.5 V t                 | •         |            | 2.8           | 3.6        | 6 mA   |  |

| 100                                  | current                          | DV <sub>DD</sub> current-<br>DI <sub>CC</sub> | CS = DGND                                                               | , 7.0 D = 0.0 V t                                    | .o 4.o v, |            | 1.2           | 2          | 1117 ( |  |

| 1                                    |                                  |                                               | For all digital in                                                      | puts DV <sub>DD</sub> or                             | SCLK ON   |            | 175           | 240        |        |  |

| ICC(SW)                              | Softwarpower-do                  | owpowerupplyurrent                            | DGND, $\overline{CS} = DV_{DD}$ ,<br>$AV_{DD} = 5.5 \text{ V}$ SCLK OFF |                                                      | SCLK OFF  |            | 20            |            | μA     |  |

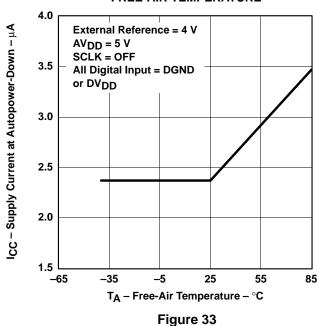

| I <sub>CC(Autodown)</sub>            | Autopower-down power supply      |                                               | For all digital in DGND, AVDD:                                          |                                                      | SCLK ON   |            | 175           | 230        | μΑ     |  |

| OO(Adiodowii)                        | current                          |                                               | External reference SCLK OFF                                             |                                                      |           | 20         |               | F          |        |  |

| Operating temp                       | erature                          |                                               | C suffix                                                                |                                                      | 0         |            | 70            | °C         |        |  |

|                                      |                                  |                                               | I suffix                                                                |                                                      | -40       |            | 85            |            |        |  |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $T_A = 25$ °C.

## TLC3544, TLC3548 5-V ANALOG, 3-/5-V DIGITAL, 14-BIT, 200-KSPS, 4-/8-CHANNELS SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH 0-5 V (PSEUDODIFFERENTIAL) INPUTS

SLAS266C - OCTOBER 2000 - REVISED MAY 2003

general electrical characteristics over recommended operating free-air temperature range, single-ended input, normal long sampling, 200 KSPS, AV $_{\rm DD}$  = 5 V, external reference (V $_{\rm REFP}$  = 4 V, V $_{\rm REFM}$  = 0 V) or internal reference, SCLK frequency = 25 MHz, fixed channel at CONV mode 00, analog input signal source resistance = 25  $\Omega$  (unless otherwise noted) (continued)

|                   | PARAMETER                                  | TEST CONDITIONS                                                                                                                              | MIN  | TYP†  | MAX      | UNIT   |

|-------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------|--------|

| Resolution        | n                                          |                                                                                                                                              | 14   |       |          | bits   |

| Analog In         | put                                        |                                                                                                                                              |      |       |          |        |

| Voltage rar       | nge                                        |                                                                                                                                              | 0 Re |       | eference | V      |

| Leakage c         | urrent                                     |                                                                                                                                              |      | 0.01  | 0.05     | μΑ     |

| Capacitano        | ce                                         |                                                                                                                                              |      |       | 30       | pF     |

| Reference         | •                                          |                                                                                                                                              |      |       |          | -      |

|                   | Internal reference voltage                 |                                                                                                                                              | 3.85 | 4     | 4.07     | V      |

|                   | Internal reference temperature coefficient |                                                                                                                                              |      | 100   |          | ppm/°C |

|                   | Internal reference source current          |                                                                                                                                              |      | 1.8   | 2.5      | mA     |

|                   | Internal reference startup time            |                                                                                                                                              |      | 20    |          | ms     |

| VREFP             | External positive reference voltage        |                                                                                                                                              | 3    |       | 5        | V      |

| VREFM             | External negative reference voltage        |                                                                                                                                              | 0    | AGND  |          | V      |

|                   |                                            | No conversion (AV <sub>DD</sub> = 5 V,<br>$\overline{\text{CS}} = \text{DV}_{\text{DD}}$ , SCLK = DGND)                                      | 100  |       |          | МΩ     |

|                   | External reference input impedance         | Normal long sampling (AV <sub>DD</sub> = 5 V,<br>CS = DGND, SCLK = 25 MHz,<br>External conversion clock)                                     | 8.3  | 12.5  |          | kΩ     |

|                   |                                            | No conversion (V <sub>REFP</sub> = AV <sub>DD</sub> = 5 V,<br><u>V<sub>REFM</sub></u> = AGND, External reference,<br>CS = DV <sub>DD</sub> ) |      | 1.5   |          | μА     |

|                   | External reference current                 | Normal long sampling (AV <sub>DD</sub> = 5 V,<br>CS = DGND, SCLK = 25 MHz external<br>conversion clock at V <sub>REF</sub> = 5 V)            |      | 0.4   | 0.6      | mA     |

| Throughp          | ut Rate                                    |                                                                                                                                              |      |       |          |        |

| f                 | Internal oscillation frequency             | DV <sub>DD</sub> = 2.7 V to 5.5 V                                                                                                            | 6.5  |       |          | MHz    |

|                   |                                            | Internal OSC, 6.5 MHz minute                                                                                                                 |      |       | 2.785    |        |

| t(conv)           | Conversion time                            | Conversion clock is external source,<br>SCLK = 25 MHz (see Note 1)                                                                           |      | 2.895 |          | μs     |

|                   | Acquisition time                           | Normal short sampling                                                                                                                        |      | 1.2   |          | μs     |

|                   | Throughput rate (see Note 2)               | Normal long sampling, fixed channel in mode 00 or 01                                                                                         | 200  |       |          | KSPS   |

| DC Accura         | acy—Normal Long Sampling                   | ·                                                                                                                                            | •    |       |          | -      |

| EL                | Integral linearity error                   | See Note 3                                                                                                                                   | -1   | ±0.5  | 1        | LSB    |

| ED                | Differential linearity error               |                                                                                                                                              | -1   | ±0.5  | 1        | LSB    |

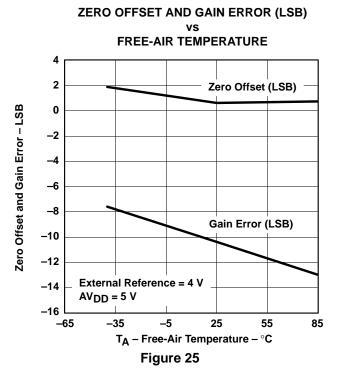

| EO                | Zero offset error                          | See Note 4                                                                                                                                   | -3   | ±0.6  | 3        | LSB    |

| E <sub>(g+)</sub> | Gain error                                 | See Note 4                                                                                                                                   | 0    | 5     | 12       | LSB    |

$\overline{\dagger}$  All typical values are at  $T_A = 25^{\circ}$ C.

NOTES: 1. Conversion time  $t_{(CONV)} = (18x4 / SCLK) + 15 \text{ ns.}$

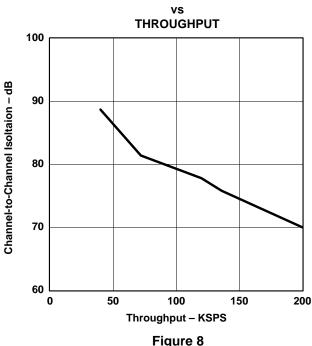

- 2. This is for a fixed channel in conversion mode 00 or 01. When switching the channels, additional multiplexer setting time is required to overcome the memory effect of the charge redistribution DAC (refer to Figure 8).

- 3. Linear error is the maximum deviation from the best fit straight line through the A/D transfer characteristics.

- 4. Zero offset error is the difference between 0000000000000 and the converted output for zero input voltage; gain error is the difference between 1111111111111 and the converted output for full-scale input voltage. The full-scale input voltage is equal to the reference voltage being used.

## TLC3544, TLC3548 5-V ANALOG, 3-/5-V DIGITAL, 14-BIT, 200-KSPS, 4-/8-CHANNELS SERIAL ANALOG-TO-DIGITAL CONVÉRTERS WITH 0-5 V (PSEUDODIFFERENTIAL) INPUTS

SLAS266C - OCTOBER 2000 - REVISED MAY 2003

general electrical characteristics over recommended operating free-air temperature range, single-ended input, normal long sampling, 200 KSPS, AV $_{DD}$  = 5 V, external reference (V $_{REFP}$  = 4 V, V $_{REFM}$  = 0 V) or internal reference, SCLK frequency = 25 MHz, fixed channel at CONV mode 00, analog input signal source resistance = 25  $\Omega$  (unless otherwise noted) (continued)

|                                  | PARAMETER                                        | TEST CONDITIONS                                              | MIN  | TYP <sup>†</sup> | MAX      | UNIT       |  |

|----------------------------------|--------------------------------------------------|--------------------------------------------------------------|------|------------------|----------|------------|--|

| DC Accu                          | racy—Normal Short Sampling                       |                                                              |      |                  |          |            |  |

| EL                               | Integral linearity error                         | See Note 3                                                   |      | ±0.8             |          | LSB        |  |

| ED                               | Differential linearity error                     |                                                              |      | ±0.6             |          | LSB        |  |

| EO                               | Zero offset error                                | See Note 4                                                   | -3   | ±0.6             | 3        | LSB        |  |

| E <sub>(g+)</sub>                | Gain error                                       | See Note 4                                                   | 0    | 5                | 12       | LSB        |  |

| AC Accu                          | racy—Normal Long Sampling                        |                                                              |      |                  | <u> </u> |            |  |

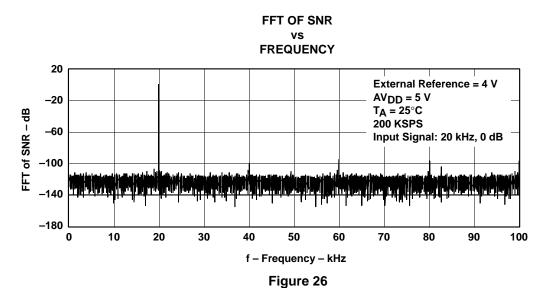

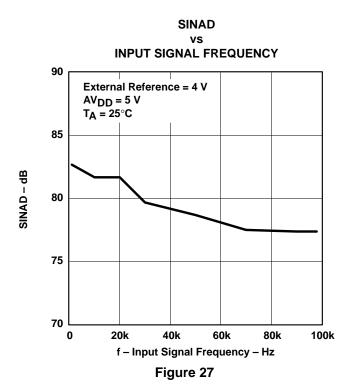

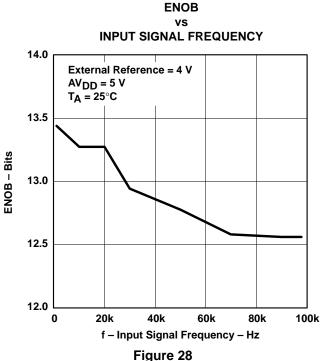

| SINAD                            | Cianal to paige ratio , distantian               | f <sub>i</sub> = 20 kHz                                      | 78.6 | 80.8             |          | 40         |  |

| SINAD                            | Signal-to-noise ratio + distortion               | f <sub>i</sub> = 100 kHz                                     |      | 77.6             |          | dB         |  |

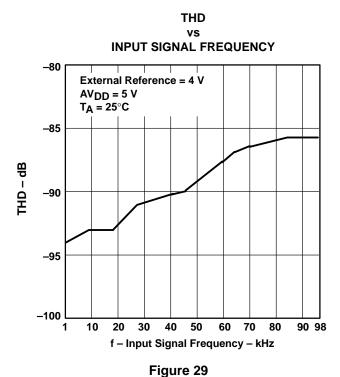

| THD                              | Total harmonia distortion                        | f <sub>i</sub> = 20 kHz                                      |      | -95              | -90      | dB         |  |

| IHU                              | Total harmonic distortion                        | f <sub>i</sub> = 100 kHz                                     |      | -88              |          | ав         |  |

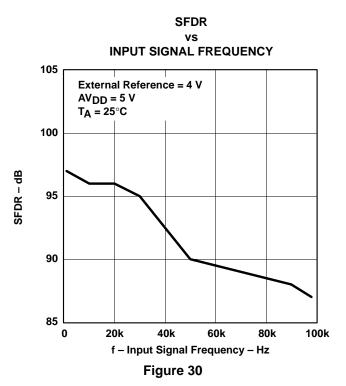

| CEDB                             | Courieus free dunamia range                      | f <sub>i</sub> = 20 kHz                                      | 90   | 97               |          | 40         |  |

| SFDR                             | Spurious free dynamic range                      | f <sub>i</sub> = 100 kHz                                     |      | 89               |          | dB         |  |

| ENOR                             | Effective number of hite                         | f <sub>i</sub> = 20 kHz                                      | 12.8 | 13.1             |          | Dita       |  |

| ENOB                             | Effective number of bits                         | f <sub>i</sub> = 100 kHz                                     |      | 12.6             |          | Bits       |  |

| CNID                             | Circulto naine natio                             | f <sub>i</sub> = 20 kHz                                      | 79   | 81               |          | <b>4</b> D |  |

| SNR                              | Signal-to-noise ratio                            | f <sub>i</sub> = 100 kHz                                     |      | 78               |          | dB         |  |

|                                  | Channel-to-channel isolation (see Notes 2 and 5) | Fixed channel in conversion mode 00, f <sub>i</sub> = 35 kHz |      | 100              |          | dB         |  |

|                                  | Analas isput has duidth                          | Full power bandwidth, -1 dB                                  |      | 2                |          | NAL 1-     |  |

|                                  | Analog input bandwidth                           | Full power bandwidth, -3 dB                                  |      | 2.5              |          | MHz        |  |

| AC Accu                          | racy—Normal Short Sampling                       | •                                                            |      |                  |          |            |  |

| SINAD                            | Signal-to-noise ratio + distortion               | rel to poice ratio L distortion   fi = 20 kHz                |      | 78.9             |          | dB         |  |

| SINAD                            | Signal-to-hoise ratio + distortion               | $f_i = 100 \text{ kHz}$                                      | 77.6 |                  |          | uБ         |  |

| THD                              | Total harmonic distortion                        | $f_i = 20 \text{ kHz}$                                       |      | -95              |          | dB         |  |

| טווו                             | Total Harmonic distortion                        | $f_i = 100 \text{ kHz}$                                      |      | -88              |          | uБ         |  |

| SNR                              | Signal to paiga ratio                            | $f_i = 20 \text{ kHz}$                                       | 79   |                  |          | dB         |  |

| SINK                             | Signal-to-noise ratio                            | $f_i = 100 \text{ kHz}$                                      |      | 78               |          | uБ         |  |

| ENOB                             | Effective number of bits                         | f <sub>i</sub> = 20 kHz                                      |      | 12.8             |          | Bits       |  |

| LNOB                             | Ellective fluitiber of bits                      | $f_i = 100 \text{ kHz}$                                      |      | 12.6             |          | סווס       |  |

| CEDD Countains for a description |                                                  | $f_i = 20 \text{ kHz}$                                       |      | 97               |          | ٩D         |  |

| SFDR                             | Spurious free dynamic range                      | f <sub>i</sub> = 100 kHz                                     | 89   |                  |          | dB         |  |

|                                  | Channel-to-channel isolation (see Notes 2 and 5) | Fixed channel in conversion mode 00, f <sub>i</sub> = 35 kHz |      | 100              |          | dB         |  |

|                                  | Analog input bandwidth                           | Full power bandwidth, -1 dB                                  |      | 2                |          | MHz        |  |

|                                  | Analog Input bandwidth                           | Full power bandwidth, -3 dB                                  |      | 2.5              |          | 1711 12    |  |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $T_A = 25$ °C.

NOTES: 2. This is for a fixed channel in conversion mode 00 or 01. When switching the channels, additional multiplexer setting time is required to overcome the memory effect of the charge redistribution DAC (refer to Figure 8).

- 3. Linear error is the maximum deviation from the best fit straight line through the A/D transfer characteristics.

- 4. Zero offset error is the difference between 0000000000000 and the converted output for zero input voltage; gain error is the difference between 111111111111 and the converted output for full-scale input voltage. The full-scale input voltage is equal to the reference voltage being used.

- 5. It is measured by applying a full-scale of 35 kHz signal to other channels and determining how much the signal is attenuated in the channel of interest. The converter samples this examined channel continuously. The channel-to-channel isolation is degraded if the converter samples different channels alternately (refer to Figure 8).

# TLC3544, TLC3548 5-V ANALOG, 3-/5-V DIGITAL, 14-BIT, 200-KSPS, 4-/8-CHANNELS SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH 0-5 V (PSEUDODIFFERENTIAL) INPUTS

SLAS266C - OCTOBER 2000 - REVISED MAY 2003

# timing requirements over recommended operating free-air temperature range, $AV_{DD} = 5 \text{ V}$ , $V_{REFM} = 0 \text{ V}$ , $V_{REFM} = 0$

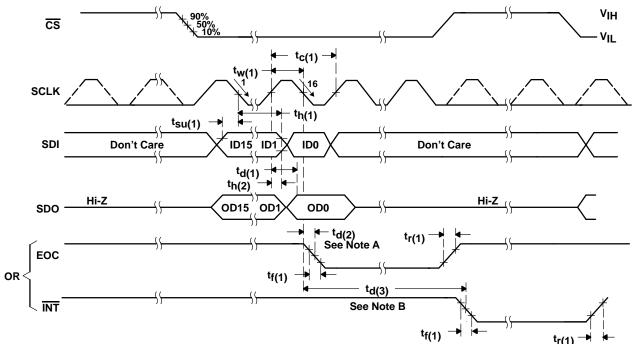

#### SCLK, SDI, SDO, EOC and INT

|                                                                                                                                          | PARAMETERS                                                                              | MIN                      | TYP MAX | UNIT                    |                   |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------|---------|-------------------------|-------------------|

|                                                                                                                                          | DV <sub>D</sub>                                                                         |                          | 100     |                         |                   |

| <sup>t</sup> c(1)                                                                                                                        | Cycle time of SCLK at 25-pF load                                                        | DV <sub>DD</sub> = 5 V   | 40†     |                         | ns                |

| t <sub>w(1)</sub>                                                                                                                        | Pulse width, SCLK high time at 25-pF load                                               |                          | 40%     | 60%                     | t <sub>c(1)</sub> |

|                                                                                                                                          | Pire time for INT FOO at 40 of lead                                                     | $DV_{DD} = 5 V$          |         | 6                       |                   |

| tr(1)                                                                                                                                    | Rise time for INT, EOC at 10-pF load                                                    | DV <sub>DD</sub> = 2.7 V |         | 10                      | ns                |

|                                                                                                                                          | 5 H 5                                                                                   | $DV_{DD} = 5 V$          |         | 6                       |                   |

| <sup>t</sup> f(1)                                                                                                                        | Fall time for INT, EOC at 10-pF load                                                    | DV <sub>DD</sub> = 2.7 V |         | 10                      | ns                |

| t <sub>su(1)</sub>                                                                                                                       | Setup time, new SDI valid (reaches 90% final level) before falling edge of sload        | 6                        | -       | ns                      |                   |

| <sup>t</sup> h(1)                                                                                                                        | Hold time, old SDI hold (reaches 10% of old data level) after falling edge o 25-pF load | f SCLK, at               | 0       | -                       | ns                |

|                                                                                                                                          | Delay time, new SDO valid (reaches 90% of final level) after SCLK rising                | DV <sub>DD</sub> = 5 V   | 0       | 10                      |                   |

| <sup>t</sup> d(1)                                                                                                                        | edge, at 10-pF load                                                                     | DV <sub>DD</sub> = 2.7 V | 0       | 23‡                     | ns                |

| <sup>t</sup> h(2)                                                                                                                        | Hold time, old SDO hold (reaches 10% of old data level) after SCLK rising load          | 0                        | -       | ns                      |                   |

| td(2) Delay time, delay from sixteenth SCLK falling edge to EOC falling edge, normal sampling, at 10-pF load                             |                                                                                         |                          |         | 6                       | ns                |

| Delay time, delay from the sixteenth falling edge of SCLK to INT falling edge, at 10-pF load [see the (‡) double dagger note and Note 6] |                                                                                         |                          |         | t <sub>(conv)</sub> + 6 | μs                |

<sup>&</sup>lt;sup>†</sup> The minimum pulse width of SCLK high is 12.5 ns. The minimum pulse width of SCLK low is 12.5 ns.

NOTE 6: For normal short sampling, t<sub>d(3)</sub> is the delay from 16th falling edge of SCLK to INT falling edge.

For normal long sampling, t<sub>d(3)</sub> is the delay from 48th falling edge of SCLK to the falling edge of INT.

Conversion time, t<sub>(CONV)</sub> is equal to 18×OSC + 15 ns when using internal OSC as conversion clock, or 72×t<sub>C(1)</sub> + 15 ns when external SCLK is conversion clock source.

<sup>‡</sup> Specified by design

NOTES: A. For normal long sampling,  $t_{d(2)}$  is the delay time of  $\overline{\text{EOC}}$  low after the falling edge of 48th SCLK. B. For normal long sampling,  $t_{d(3)}$  is the delay time of  $\overline{\text{INT}}$  low after the falling edge of 48th SCLK.

For normal long sampling, t<sub>d(3)</sub> is the delay time of INT low after the falling edge of 48th SCLK.

— — — The dotted line means signal may or may not exist, depending on application. It must be ignored.

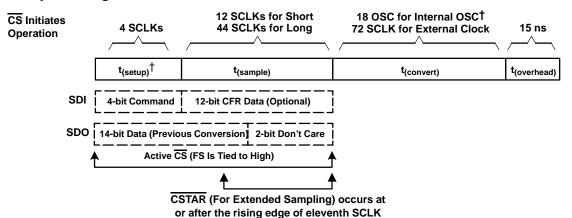

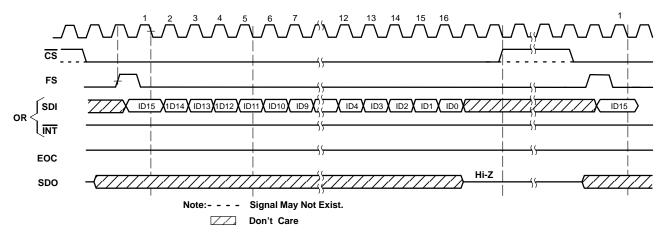

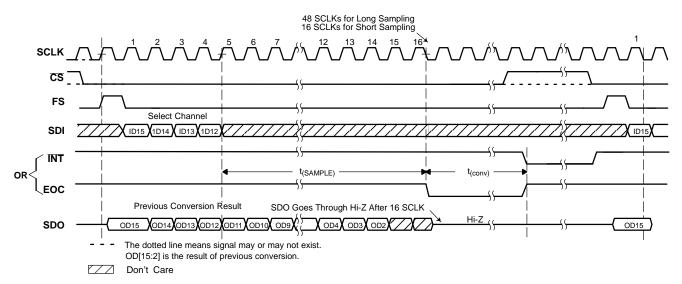

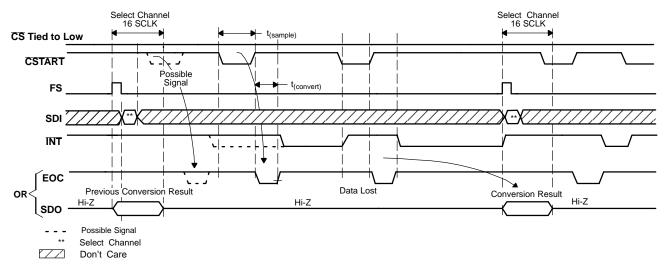

Normal sampling mode, CS initiates the conversion, FS must be tied to high. When CS is high, SDO is in Hi-Z; all inputs (FS, SCLK, SDI) are inactive and are ignored.

Figure 1. Critical Timing for SCLK, SDI, SDO, EOC and INT

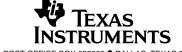

# timing requirements over recommended operating free-air temperature range, $AV_{DD} = 5 \text{ V}$ , $V_{REFP} = 5 \text{ V}$ , $V_{REFM} = 0 \text{ V}$ , $V_{REFM} = 0$

#### **CS** trigger

|                                                                                                                             | PARAMETERS                                                                            | MIN               | TYP | MAX | UNIT |                   |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------|-----|-----|------|-------------------|

| t <sub>su(2)</sub>                                                                                                          | Setup time, CS falling edge before SCLK rising edge, at 25-pF load                    |                   | 12  |     |      | ns                |

| t <sub>d(4)</sub> Delay time, delay time from 16th SCLK falling edge to $\overline{\text{CS}}$ rising edge, at 25-pF load ‡ |                                                                                       |                   |     |     |      | ns                |

| t <sub>w(2)</sub> Pulse width, $\overline{\text{CS}}$ high time at 25-pF load                                               |                                                                                       |                   |     |     |      | t <sub>c(1)</sub> |

|                                                                                                                             | Delay time, delay from CS falling edge to MSB of SDO valid (reaches 90%               | $DV_{DD} = 5 V$   | 0   |     | 12   |                   |

| <sup>t</sup> d(5)                                                                                                           | final level), at 10-pF load                                                           | $DV_{DD} = 2.7 V$ | 0   |     | 30†  | ns                |

| <sup>t</sup> d(6)                                                                                                           | t <sub>d(6)</sub> Delay time, delay from CS rising edge to SDO 3-state, at 10-pF load |                   |     |     | 6    | ns                |

| + · /=>                                                                                                                     | Delay time, delay from CS falling edge to INT rising edge, at 10-pF load              | $DV_{DD} = 5 V$   | 0   |     | 6    | ns                |

| <sup>t</sup> d(7)                                                                                                           | Delay time, delay from CS failing edge to INT fising edge, at 10-pr load              |                   | 0   |     | 16†  | 115               |

<sup>†</sup> Specified by design

<sup>‡</sup> For normal short sampling, t<sub>d</sub>(4) is the delay time from 16th SCLK falling edge to  $\overline{CS}$  rising edge. For normal long sampling, t<sub>d</sub>(4) is the delay time from 48th SCLK falling edge to  $\overline{CS}$  rising edge.

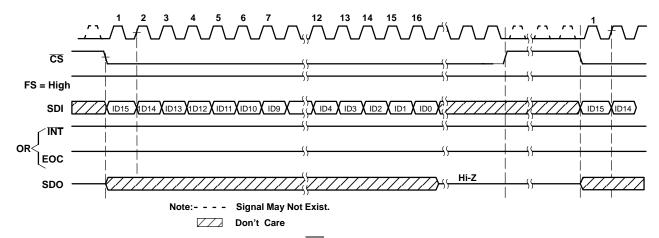

NOTE A: ———— The dotted line means signal may or may not exist, depending on application. It must be ignored.

Normal sampling mode,  $\overline{CS}$  initiates the conversion, FS must be tied to high. When  $\overline{CS}$  is high, SDO is in Hi-Z, all inputs (FS, SCLK, SDI) are inactive and are ignored. Parts with date code earlier than 13XXXXX have these discrepancies:

(Date code is a 7 digit code next to the TI where the first digit indicates the year and the second digit is the month of production. 13, in this case, is 2001 and the month of March.)

FS is not ignored even if the device is in microcontroller mode (CS triggered).

FS must be tied to DV<sub>DD</sub>.

Figure 2. Critical Timing for CS Trigger

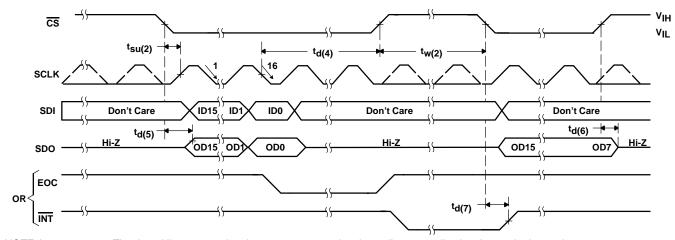

timing requirements over recommended operating free-air temperature range,  $AV_{DD} = 5 \text{ V}$ ,  $V_{REFM} = 0 \text{ V}$ ,  $V_{REFM} = 0$

#### FS trigger

|                    | PARAMETERS                                                                                    |                          |                        | TYP               | MAX                       | UNIT  |

|--------------------|-----------------------------------------------------------------------------------------------|--------------------------|------------------------|-------------------|---------------------------|-------|

| <sup>t</sup> d(8)  | Delay time, delay from CS falling edge to FS rising edge, at 25-p                             | F load                   | 0.5                    |                   |                           | tc(1) |

| t <sub>su(3)</sub> | Setup time, FS rising edge before SCLK falling edge, at 25-pF lo                              | oad                      | 0.25×t <sub>c(1)</sub> |                   | $0.5 \times t_{c(1)} + 5$ | ns    |

| t <sub>w(3)</sub>  |                                                                                               |                          |                        | <sup>t</sup> c(1) | 1.25×t <sub>c(1)</sub>    | ns    |

|                    | Delay time, delay from FS rising edge to MSB of SDO valid                                     |                          |                        |                   | 26†                       |       |

| <sup>t</sup> d(9)  | (reaches 90% final level) at 10-pF load                                                       | DV <sub>DD</sub> = 2.7 V |                        |                   | 30†                       | ns    |

| <sup>t</sup> d(10) | t <sub>d(10)</sub> Delay time, delay from FS rising edge to next FS rising edge at 25-pF load |                          |                        |                   |                           | μs    |

|                    | Delay time, delay from FS rising edge to INT rising edge at                                   |                          | 0                      |                   | 6†                        |       |

| <sup>t</sup> d(11) | 10-pF load                                                                                    | DV <sub>DD</sub> = 2.7 V |                        |                   | 16†                       | ns    |

<sup>†</sup>Specified by design

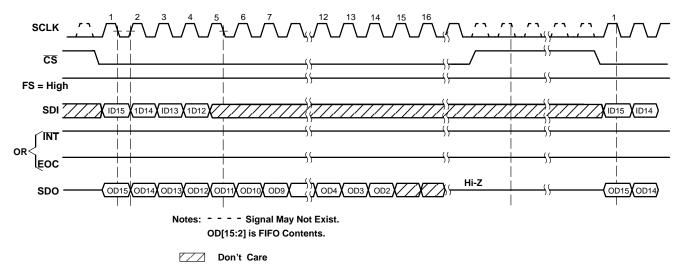

NOTE A: --- The dotted line means signal may or may not exist, depending on application. It must be ignored.

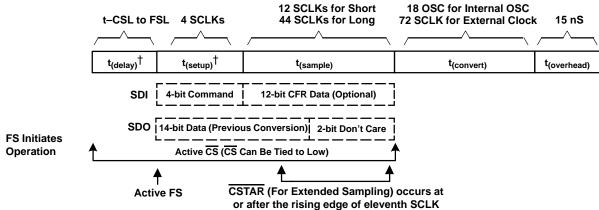

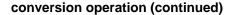

Normal sampling mode, FS initiates the conversion,  $\overline{CS}$  can be tied to low. When  $\overline{CS}$  is high, SDO is in Hi-Z, all inputs (FS, SCLK, SDI) are inactive and are ignored.

Parts with date code earlier than 13XXXXX have these discrepancies:

(Date code is a 7 digit code next to the TI where the first digit indicates the year and the second digit is the month of production. 13, in this case, is 2001 and the month of March.)

SDO MSB (OD[15]) comes out from the falling edge of  $\overline{\text{CS}}$  instead of FS rising edge in DSP mode (FS triggered).

Figure 3. Critical Timing for FS Trigger

timing requirements over recommended operating free-air temperature range,  $AV_{DD} = 5 \text{ V}$ ,  $V_{REFP} = 5 \text{ V}$ ,  $V_{REFM} = 0 \text{ V}$ , SCLK frequency = 25 MHz (unless otherwise noted) (continued)

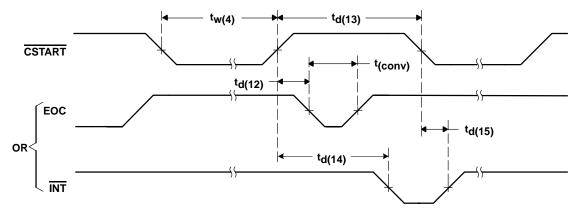

#### **CSTART** trigger

|                    | PARAMETERS                                                                                            | MIN                 | TYP           | MAX        | UNIT |

|--------------------|-------------------------------------------------------------------------------------------------------|---------------------|---------------|------------|------|

| <sup>t</sup> d(12) | Delay time, delay from CSTART rising edge to EOC falling edge, at 10-pF load                          | 0                   | 15            | 21         | ns   |

| t <sub>W</sub> (4) | Pulse width $\overline{\text{CSTART}}$ low time: $t_{W(L)}(\overline{\text{CSTART}})$ , at 25-pF load | t(sample - ref)+0.4 | Note 7        |            | μs   |

| <sup>t</sup> d(13) | Delay time, delay from CSTART rising edge to CSTART falling edge, at 25-pF load                       | t(conv) +15         | Notes 7 and 8 |            | ns   |

| <sup>t</sup> d(14) | Delay time, delay from CSTART rising edge to INT falling edge, at 10-pF load                          | t(conv) +15         | Notes 7 and 8 | t(conv)+21 | ns   |

| <sup>t</sup> d(15) | Delay time, delay from CSTART falling edge to INT rising edge, at 10-pF load                          | 0                   |               | 6          | μs   |

#### NOTES: 7.

- The pulse width of CSTART must be not less than the required sampling time. The delay from CSTART rising edge to following CSTART falling edge must not be less than the required conversion time. The delay from CSTART rising edge to the INT falling edge is equal to the conversion time.

- 8. The maximum rate of SCLK is 25 MHz for normal long sampling and 10 MHz for normal short sampling.

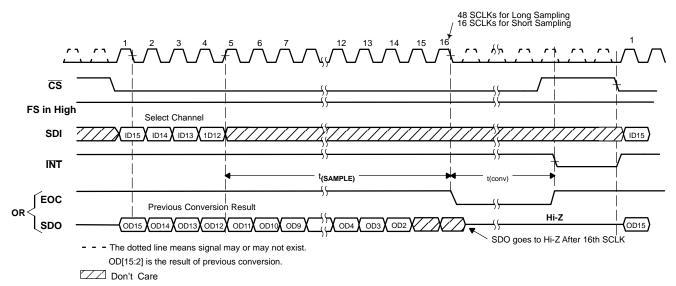

**Extended Sampling**

Figure 4. Critical Timing for Extended Sampling (CSTART Trigger)

#### detailed description

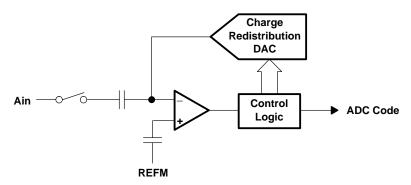

#### converter

The converters are a successive-approximation ADC utilizing a charge redistribution DAC. Figure 5 shows a simplified block diagram of the ADC. The sampling capacitor acquires the signal on Ain during the sampling period. When the conversion process starts, the control logic directs the charge redistribution DAC to add and subtract fixed amounts of charge from the sampling capacitor to bring the comparator into a balanced condition. When balanced, the conversion is complete and the ADC output code is generated.

#### detailed description (continued)

Figure 5. Simplified Block Diagram of the Successive-Approximation System

#### analog input range and internal test voltages

TLC3548 has eight analog inputs (TLC3544 has four) and three test voltages. The inputs are selected by the analog multiplexer according to the command entered (see Table 1). The input multiplexer is a break-before-make type to reduce input-to-input noise injection resulting from channel switching.

The TLC3544 and TLC3548 are specified for a unipolar input range of 0-V to 4-V when the internal reference is selected, and 0-V to 5-V when an external 5-V reference is used.

#### analog input mode

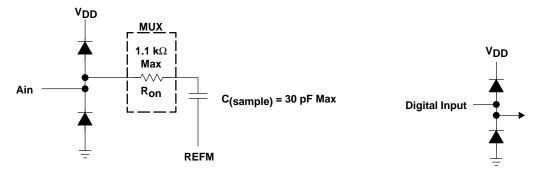

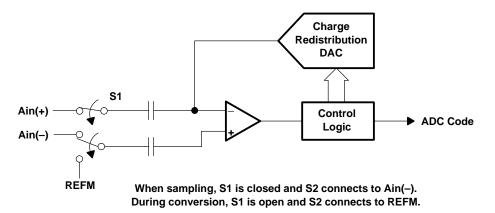

Two input signal modes can be selected: single-ended input and pseudodifferential input.

Figure 6. Simplified Pseudodifferential Input Circuit

Pseudodifferential input refers to the negative input, Ain(-); its voltage is limited in magnitude to  $\pm 0.2$  V. The input frequency limit of Ain(-) is the same as the positive input Ain(+). This mode is normally used for ground noise rejection or dc bias offset.

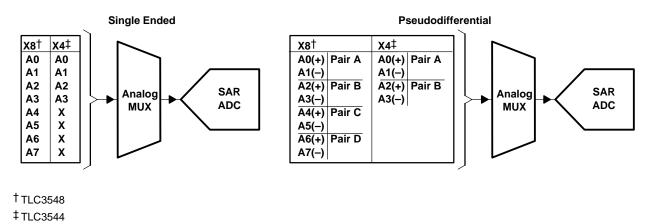

When pseudodifferential mode is selected, only two analog input channel pairs are available for the TLC3544 and four channel pairs for the TLC3548, because half the inputs are used as the negative input (see Figure 7).

#### analog input mode (continued)

Figure 7. Pin Assignment of Single-Ended Input vs Pseudodifferential Input

#### reference voltage

There is a built-in 4-V reference. If the internal reference is used, REFP is internally set to 4-V and REFM is set to 0-V. The external reference can be applied to the reference-input pins (REFP and REFM) if programmed (see Table 2). The REFM pin should connect to analog ground. REFP can be 3-V to 5-V. Install decoupling capacitors (10  $\mu$ F in parallel with 0.1  $\mu$ F) between REFP and REFM. Install compensation capacitors (10  $\mu$ F in parallel with 0.1  $\mu$ F for internal reference, 0.1  $\mu$ F only for external reference) between BGAP and AGND.

#### detailed description (continued)

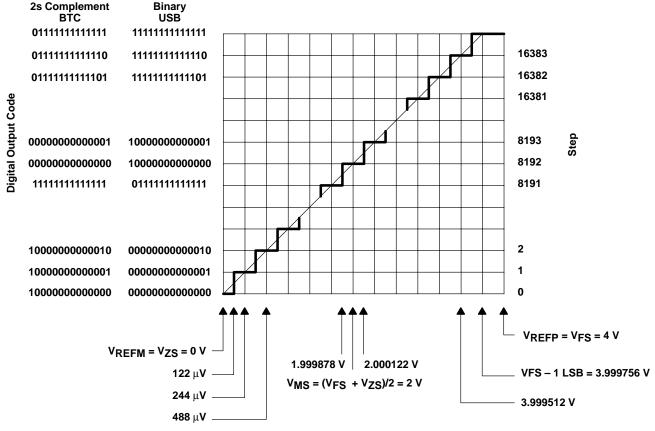

#### ideal conversion characteristics

#### **Unipolar Analog Input Voltage**

#### 1 LSB = 244 μV

#### data format

| INP       | UT DATA FORMAT (BINARY)                       | OUTPUT DATA       | FORMAT READ CONVERSION/FIFO |

|-----------|-----------------------------------------------|-------------------|-----------------------------|

| MSB       | LSB                                           | MSB               | LSB                         |

| ID[15:12] | ID[11:0]                                      | OD[15:2]          | OD[1:0]                     |

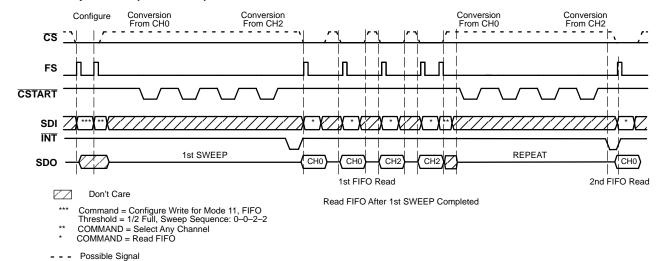

| Command   | Configuration data field or filled with zeros | Conversion result | Don't Care                  |